Тестирование моделей микросхем

Сценарий

Тенденции в сетевой отрасли, включая развитие облачных вычислений и виртуализации сетевых функций (NFV), порождают все более высокие требования к емкости сетей. Для выполнения этих требований производители сетевого оборудования и интегральных микросхем должны выпускать устройства, поддерживающие множество портов и основанные на современных решениях типа system-

Разработка SoC, способных обрабатывать терабиты трафика, поступающего через сотни портов, на скоростях до 100 Гбит/с — длительный процесс. Но все основные производители микросхем стараются ускорить выполнение циклов разработки, поскольку нужно быстро выводить на рынок новые изделия. Затраты на исправление ошибок в микросхеме после ее выпуска могут составлять миллионы долларов. Чтобы избежать столь значительных расходов, необходимо тщательно тестировать модели микросхем до их реализации в кремнии.

Решение Ixia

Компания Ixia выпускает IxVerify — единственное в отрасли тестовое решение, специально разработанное для аттестации моделей микросхем до их реализации в кремнии. Предлагая это решение, компания Ixia и ее партнеры преобразуют рынок САПР электроники (EDA). Решение IxVerify, в котором технология виртуализации обеспечивает сокращение затрат на разработку микросхем и повышение гибкости процессов разработки, может использоваться совместно с имеющимися у заказчиков системами EDA. Данное решение позволяет применять новые и улучшенные методики тестирования, упрощающие процедуры испытаний моделей микросхем.

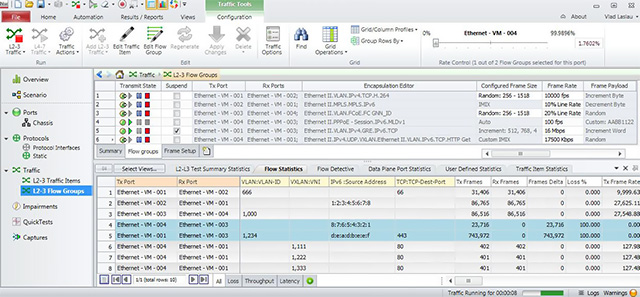

Решение IxVerify может генерировать большие объемы тестового трафика Ethernet с использованием сотен готовых шаблонов пакетов для проверки работы протоколов Ethernet и TCP/IP. При своей способности запускать сотни виртуализированных тестовых портов одновременно IxVerify предоставляет уникальную возможность динамически управлять формой трафика (traffic shaping), чтобы гарантировать отсутствие потерь пакетов при максимальной скорости эмуляции.

Информация о трафике в интерфейсе IxVerify

IxVerify — идеальное решение для уменьшения рисков, связанных с разработкой сложных сетевых микросхем. Оно гарантирует ускорение выпуска на рынок сетевых устройств нового поколения.